37 Принципы организации контроля функционирования ЭВМ.

Классификация методов контроля. Контроль оперативной памяти.

В производимых ЭВМ

преобразованиях информации очень важна их достоверность, для этого используются

различные методы контроля функционирования ЭВМ. Наличие системного контроля

закладывается на этапе проектирования ЭВМ. Системный контроль тесно взаимодействует

с системами диагностики. Вне зависимости от того, как

именно реализуется контроль и исправление ошибок, в основе их всегда лежит

введение некоторого рода избыточности.

Аппаратный:

Наличие аппаратного контроля

означает, что операционный контроль осуществляется непосредственно во время

процесса выполнения операций. При введении аппаратного контроля вводится

избыточность разрядов (пространственная).

Должен обеспечивать:

1)

контроль данных

2)

контроль команд – имеется дескриптор выполняемости, если он взведен – это

команда, иначе – данные.

3)

контроль адресов – не выходит ли адрес за пределы сегмента (при

сегментно-страничной организации)

Оперативный контроль

– это контроль, который производится постоянно:

-

сквозной (контролируются все устройства)

-

локальный (контролируется конкретное устройство)

Встроенный контроль

– контроль, при котором в систему встраиваются специальные датчики, которые

контролируют электрические параметры. Чаще всего используются в источниках

питания.

Тестовый –

различного рода тестирование:

-

контролирующий – тестовые программы с заранее известным результатом

-

диагностирующий – тестовые программы, выявляющие место сбоя

Программно-логический

контроль:

Контроль основан на формировании

результата выполнения операции 2-мя различными независимыми путями и дальнейшем

их сравнении. Необходимо выявлять как случайные ошибки, так и ошибки вызванные

отказами.

Можно выделить следующие методы:

- метод программного счета. Одна

и та же программа прокручивается несколько раз, зачастую достаточно двух

прогонов. Плохо определяются ошибки вызванные отказами.

- метод обратного счета. Сначала

решается прямая задача, затем обратная, при этом возникает необходимость писать

2 программы, сравнивать результаты прямого и обратного счета с учетом

погрешностей. Выгоден только при небольших размерах обратного алгоритма.

- решение задачи по двум

алгоритмам: более и менее точному. Недостатки: необходимость написания двух

программ; собственно, поиск второго, более простого, алгоритма.

- метод контрольных точек. В этом

случае в программу вводится процедура для выполнения контроля. Этот метод

реагирует не на случайные ошибки, а на отказ.

2-ой и 3-ий методы

взаимодополняют друг друга.

Для реализации контроля

вводится избыточность:

1)

временная – увеличение времени выполнения операций для контроля.

2)

пространственная – увеличение разрядности данных для контроля.

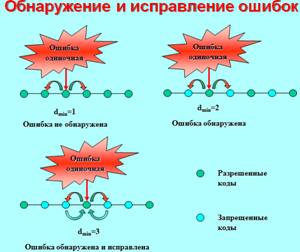

Обнаружение и исправление

ошибок

При работе с полупроводниковой

памятью не исключено возникновение различного рода отказов и сбоев. Причиной отказов

могут быть производственные дефекты, повреждение микросхем или их

физический износ. Проявляются отказы в том, что в отдельных разрядах одной или

нескольких ячеек постоянно считывается 0 или 1, вне зависимости от реально

записанной туда информации. Сбой- это случайное событие, выражающееся в

неверном считывании или записи информации в отдельных разрядах одной или

нескольких ячеек, не связанное с дефектами микросхемы. Как отказы, так и сбои

крайне нежелательны, поэтому в большинстве систем основной памяти содержатся

схемы, служащие для обнаружения и исправления ошибок.

Рассмотрим принципы контроля,

связанные с введением избыточных данных.

На

рисунке показано, каким образом осуществляются обнаружение и исправление

ошибок. Перед записью М-разрядных данных в память производится их обработка,

обозначенная на схеме функцией «f», в результате которой формируется добавочный К-разрядный

код. В память заносятся как данные, так и этот вычисленный код, то есть (М+К)-разрядная

информация. При чтении информации повторно формируется К-разрядный код, который

сравнивается с аналогичным кодом, считанным из ячейки. Сравнение приводит к

одному из трех результатов:

- Не обнаружено ни одной ошибки. Извлеченные данные

подаются на выход памяти.

- Обнаружена

исправимая ошибка. Биты данных и

добавочного кода подаются на схему коррекции. После исправления ошибки в данных

они поступают на выход памяти.

- Обнаружена неисправимая ошибка. Выдается сообщение о неисправимой ошибке.

Коды, используемые для подобных операций, называют корректирующими

кодами или кодами с исправлением ошибок.

В основе корректирующих кодов лежит следующая идея. Для контроля

двоичного информационного кода длиной М бит добавим к ней К дополнительных

контрольных разрядов. В этом случае из возможных N = 2М"К

комбинаций интерес представляют только L = 2м последовательностей, которые называют:

разрешенными. Оставшиеся N - L последовательностей

назовем запрещенными. Если при обработке (записи в память, считывании

или передаче) разрешенной кодовой последовательности произойдут ошибки и

возникнет одна из запрещенных последовательностей, то тем самым эти ошибки

обнаруживаются. Если же ошибки превратят одну разрешенную последовательность в

другую, то такие ошибки не могут быть обнаружены. Благодаря свойствам

контрольных разрядов, характерным для конкретных методов контроля, в некоторых

случаях возможно определить не только наличие, но и местоположение ошибки, а

также произвести её коррекцию.

Простейший вид корректирующего кода основан на добавлении к

каждому байту информации одного бита паритета. Бит паритета — это

дополнительный бит, значение которого устанавливается таким, чтобы суммарное

число единиц в данных, с учетом этого дополнительного разряда, было четным

(или нечетным). При чтении из памяти вычисляется бит паритета для считанных

информационных битов, результат сравнивается с битом паритета, вычисленным при

записи и хранившимся в памяти. Метод позволяет обнаружить ошибку, если

исказилось нечетное количество битов, при четном числе ошибок метод

неработоспособен. Данный метод позволяет только обнаруживать ошибки, причём

местоположение ошибки остаётся неизвестным.

Существует более совершенный метод, основанный на

использовании битов паритета. При его использовании биты данных представляются

в виде матрицы, к каждой строке и столбцу которой добавляется бит паритета. Для

64-разрядных данных этот подход иллюстрирует таблица 1:

Недостаток рассмотренного приема в том, что он требует

большого числа дополнительных разрядов. Более эффективным представляется код,

предложенный Ричардом Хэммингом и носящий его имя (код Хэмминга).

В качестве иллюстрации использования данной концепции,

приведём код, обнаруживающий и исправляющий однобитовые ошибки в 8-разрядных

словах.

Сначала определим требуемую длину корректирующего кода. В

соответствии с рис., на вход схемы сравнения поступают два К-разрядных

значения. Сравнение производится путем поразрядной операции «исключающее ИЛИ»

(сложение по модулю 2) над входными кодами. Результатом является так называемое

слово синдрома. В зависимости от того, было ли совпадение входных кодов

или нет, соответствующий бит синдрома будет равен 0 или 1.

Слово синдрома состоит из К разрядов, то есть его

возможные значения лежат в диапазоне от 0 до 2К - 1. Значение

0 соответствует случаю, когда ошибки не обнаружено, остальные 2К

— 1 случая свидетельствуют о наличии ошибки и указывают на ее

местоположение.

Поскольку ошибка может возникнуть в любом из М битов

данных или К контрольных битов, мы должны иметь 2к - 1 > М

+ К. Это выражение позволяет определить число битов, необходимое

для исправления одиночной ошибки в М-разрядных данных. В нашем примере,

для 8-разрядных слов требуется четыре корректирующих разряда.

Для удобства будем формировать четырехразрядный

синдром со следующими характеристиками:

- Если синдром содержит все нули, значит, не обнаружено ни

одной ошибки.

- Если синдром содержит единственную единицу в одном из

разрядов, это означает, что выявлена ошибка в одном из четырех корректирующих

разрядов и никакой коррекции не требуется.

- Если в синдроме в единичное состояние

установлены несколько битов, то численное значение синдрома соответствует

позиции ошибки в данных, для исправления которой необходимо инвертировать бит

в этой позиции (нумерация с единицы!).

Для

поддержания этих свойств под контрольные разряды отводятся те биты, чьи

позиционные номера представляют собой степень числа 2 (табл. 2).

Отдельный контрольный разряд отвечает за определенные биты данных. Так,

разрядная позиция п контролируется теми битами Рi,

которые делают справедливым соотношение  = п. Например, разряд данных с позиционным номером

710 (01112) контролируется битами 4, 2 и 1 (7 = 4 + 2 +

1), а разряд с номером 1010 (10102) - битами 8 и 2 (10 =

8 + 2).

= п. Например, разряд данных с позиционным номером

710 (01112) контролируется битами 4, 2 и 1 (7 = 4 + 2 +

1), а разряд с номером 1010 (10102) - битами 8 и 2 (10 =

8 + 2).

По мере развития систем В/ВЫВ их функции

усложняются. Главная цель такого усложнения — максимальное высвобождение ЦП от

управления процессами ввода/вывода. Некоторые пути решения этой задачи уже были

рассмотрены. Следующими шагами в преодолении проблемы могут быть:

1.

Расширение возможностей МВБ и предоставление ему прав процессора со

специализированным набором команд, ориентированных на операции ввода/вывода. ЦП

дает указание такому процессору В/ВЫВ выполнить хранящуюся в памяти ВМ

программу ввода/вывода. Процессор В/ВЫВ извлекает и исполняет команды этой

программы без участия центрального процессора и прерывает ЦП только после

завершения всей программы ввода/вывода.

2. Рассмотренному в пункте 1 процессору ввода/вывода придается

собственная локальная память, при этом возможно управление множеством устройств

В/ВЫВ с минимальным привлечением ЦП.

В первом случае МВВ называют каналом

ввода/вывода (КВВ). а во втором – процессором ввода/вывода. В

принципе различие между каналом и процессором ввода/вывода достаточно условно,

поэтому в дальнейшем будем пользоваться термином «канал».

Концепция системы ввода/вывода с КВВ

характерна для больших универсальных вычислительных машин (мэйнфреймов), где

проблема эффективной организации В/ВЫВ и максимального высвобождения

центрального процессора в пользу его основной функции стоит наиболее остро.

В ВМ с каналами ввода/вывода центральный

процессор практически не участвует в непосредственном управлении внешними

устройствами, делегируя эту задачу специализированному процессору, входящему в

состав КВВ. Все функции ЦП сводятся к запуску и остановке операций в КВВ, а

также проверке состоят канала и подключенных к нему ВУ. Для этих целей ЦП

использует лишь несколько (от 4 до 7) команд ввода/вывода. Например, в IBM 360 таких команд

четыре:

■ «Начать ввод/вывод»;

■ «Остановить ввод/выводу;

■ «Проверить ввод/вывода;

■ «Проверить канал».

КВВ реализует операции В/ВЫВ путем выполнения

так называемой канальной программы. Канальные программы для каждого ВУ,

с которым предполагается обмен информацией, описывают нужную последовательность

операций ввода/вывода и хранятся в основной памяти ВМ. Роль команд в канальных

программах выполняют управляющие слова канала (УСК), структура которых

отличается от структуры обычной машинной команды. Типовое УСК содержит:

■ код операции, определяющий для

КВВ и ВУ тип операции: «Записать» (вывод информации из ОП в ВУ), «Прочитать»

(ввод информации из ВУ в ОП), «Управление» (перемещение головок НМД, магнитной

ленты и т. п.);

■ указатели — дополнительные предписания,

задающие более сложную последовательность операций В/ВЫВ, например при вводе

пропускать отдельные записи или наоборот — с помощью одной команды вводить

«разбросанный» по ОП массив как единый;

■ адрес данных, указывающий

область памяти, используемую в операции ввода/ вывода;

■ счетчик данных, хранящий

значение длины передаваемого блока данных.

Кроме того, в УСК может содержаться

идентификатор ВУ и информация о его уровне приоритета, указания по действиям,

которые должны быть произведены при возникновении ошибок и т. п.

Центральный процессор инициирует ввод/вывод

путем инструктирования канала о необходимости выполнить канальную программу,

находящуюся в ОП, и указания начального адреса этой программы в памяти ВМ. КВВ

следует этим указаниям и управляет пересылкой данных. Отметим, что пересылка

информации каналом ведется в режиме прямого доступа к памяти. ВУ

взаимодействуют с каналом, получая от него приказы. Таким образом, в ВМ с КВВ

управление вводом/выводом строится иерархическим образом. В операциях ввода/вывода

участвуют три типа устройств:

■ процессор (первый уровень управления);

■ канал ввода/вывода (второй уровень);

■ внешнее устройство (третий уровень).

Каждому типу устройств соответствует свой вид

управляющей информации:

■ процессору — команды ввода/вывода;

■ каналу - управляющие слова канала;

■ периферийному устройству - приказы.

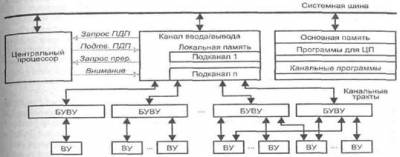

Структура ВМ с канальной системой ввода/вывода

показана на рис. 8.12.

Обмен информацией между КВВ и основной памятью

осуществляется посредством системной шины ВМ. ВУ подключаются к каналу не

непосредственно, а через блоки управления внешними устройствами (БУВУ). БУВУ

принимает от канала приказы по управлению внешним устройством (чтение, запись,

перемещение носителя или магнитной головки и т.п.) и преобразует их в сигналы

управления, свойственные данному типу ВУ. Обычно один БУВУ может обслуживать

несколько однотипных ВУ, но для подключения быстродействующих внешних устройств

Часто применяются индивидуальные блоки, управления. В свою очередь, некоторые

ВУ могут подключаться одновременно к нескольким БУВУ, Это позволяет

воспользоваться свободным трактом другого БУВУ при занятости данного БУВУ

обслуживанием одного из подключенных к нему ПУ. Физически БУВУ может быть

самостоятельным устройством или интегрирован с ВУ или каналом.

Обмен информацией между БУВУ и КВВ

обеспечивается так называемыми канальными трактами. Обычно каждое БУВУ

связано с одним из канальных трактов, но возможно также подключение блока

управления сразу к нескольким тракам, что дает возможность избежать нежелательных

задержек при занятости одного из них.

В пределах канала ввода/вывода считается, что

каждое ВУ подключено к своему подканалу. Подканалы имеют свои уникальные

логические номера, с помощью которых канальная программа адресуется к

конкретному ВУ. Физически подканал реализуется в виде участка памяти, в котором

хранятся параметры операции ввода/вывода,

выполняемой данным ВУ: текущие значения адреса и счетчика данных, код и

указатели операции ввода/вывода, адрес следующего УСК и др. Для хранения этих параметров

обычно используется локальная память канала.

Обмен информацией между ВУ и ОП, как уже

упоминалось, реализуется в режиме прямого доступа к памяти, при этом для

взаимодействия ЦП и канала задействованы сигналы «Запрос ПДП» и «Подтверждение

ПДП».

Чтобы известить ЦП об окончании текущей

канальной программы или об ошибках, возникших при ее выполнении, КВВ выдает в

ЦП сигнал «Запрос прерывания». В свою очередь, ЦП может привлечь внимание

канала сигналом «Внимание».

Способ организации взаимодействия ВУ с каналом

определяется соотношением быстродействия ОП и ВУ. По этому признаку ВУ образуют

две группы: быстродействующие (накопители на магнитных дисках (НМД), накопители

на магнитных лептах (НМЛ)) со скоростью приема и выдачи информации около 1

Мбайт/с и медленнодействующие (дисплеи, печатающие устройства и др.) со

скоростями порядка 1 Кбайт/с и менее. Быстродействие основной памяти обычно

значительно выше. С учетом производительности ВУ в КВВ реализуются два режима работы:

мультиплексный (режим разделения времени) и монопольный.

В мультиплексном режиме несколько

внешних устройств разделяют канал во времени, при этом каждое из параллельно

работающих с каналом ВУ связывается с КВВ на короткие промежутки времени только

после того, как ВУ будет готово к приему или выдаче очередной порции информации

(байта, группы байтов и т. д.). Такая схема принята в мультиплексном канале

ввода/вывода. Если в течение сеанса связи пересылается один байт или

несколько байтов, образующих одно машинное слово, канал называется байт-мультиплексным.

Канал, в котором в пределах сеанса связи пересылка данных выполняется

поблочно, носит название блок-4 мультиплексного.

В монопольном режиме после установления

связи между каналом и ВУ последнее монополизирует канал на все время до завершения

инициированной процессором канальной программы и всех предусмотренных этой

программой пересылок данных между ВУ и ОП. На все время выполнения канальной

программы канал оказывается недоступным для других ВУ. Данную процедуру

обеспечивает селекторный канал ввода/вывода. Отметим, что в

блок-мультиплексном канале в рамках сеанса связи пересылка блока осуществляется

в монопольном режиме.

Помимо указанных функций на канал

может возлагаться ряд дополнительных для минимизации участия процессора в

операциях I/O:

·

Организация

цепочки данных.

Для случаев, когда массив информации, предназначенный для операции ввода или

вывода с некоторым ПУ, не располагается в памяти подряд, а состоит из

нескольких подмассивов, размещенных в произвольно расположенных участках ОП. Чтобы

в этом случае ввод (вывод) каждого подмассива не требовал включения в программу

процессора отдельной команды ввода (вывода), а передача всех подмассивов

инициировалась одной командой процессора, канал должен допускать задание в

программе управления каналом цепочки для передачи такого составного массива.

·

Организация

пропуска информации.

При операциях I/O может

возникнуть необходимость переносить в память с носителя информации отдельные

части массива, пропуская ненужные данные.

·

Формирование

запросов прерывания от I/O. Канал должен прерыванием извещать

процессор об окончании каждой операции I/O, а также об

обнаружении ошибки или каких-либо других необычных условий, вследствие чего

произошло принудительное окончание выполняемой операции. Наряду с этим должна

иметься возможность задания прерывания на любом этапе операции I/O. Такое

прерывание называется программно-управляемым. Оно не нарушает нормальное

выполнение текущей операции I/O. Появление

запроса программно-управляемого прерывания означает, что выполнены все операции

I/O, предшествующие

в программе управления каналом этому запросу.

·

Управляющая

информация для операций I/O. В операциях I/O участвуют три

типа устройств: процессор (превый уровень управления), сопроцессор I/O (второй

уровень), ПУ (третий уровень). Каждому типу устройств соответствует

определенный вид управляющей информации: процессору – команды, сопроцессору –

управляющие слова канала (УСК), ПУ – приказы. Кроме того, в управлении I/O используются

коды состояния канала (слово состояния сопроцессора) и ПУ (байт состояний и

байты уточненного состояния). Команды I/O процессора (!)

являются привилегированными и выполняются только в состоянии «супервизор».

Классификация сопроцессоров I/O

В зависимости от соотношения быстродействия ОП и ПУ в

каналах I/O могут

реализовываться два режима работы: монопольный (селекторный), разделения

времени (мультиплексирования).

<-Монопольный режим.

После установки связи между каналом и ПУ последнее монополизирует канал на все

время, пока полностью не завершится инициированная процессором программа

управлением сопроцессором I/O

работы с данным ПУ и не будут произведены все предусмотренные этой программой

передачи данных между ОП и ПУ. На все время выполнения данной программы I/O канал оказывается занятым для

других ПУ.

Режим разделения времени ->

(мультиплексный). Несколько ПУ разделяют во времени канал I/O, при этом каждое из параллельно работающих с данным каналом

ПУ связывается с каналом на короткие промежутки времени только после того, как

ПУ подготовлено к приему или выдаче очередной порции информации. Промежуток

времени, в течение которого происходит передача информации между каналом и

подготовленным к этому ПУ, может быть назван сеансом связи. Сеансы связи

различных ПУ чередуются между собой. Во время сеанса связи одного из устройств

с каналом другие устройства могут выполнять работу не требующую использования

средств канала. В соответствии с преимущественно реализуемым режимом работы

различают каналы I/O

мультиплексный, осуществляющий мультиплексирование ПУ, и селекторный,

взаимодействующий с ПУ в монопольном режиме.

Сопроцессор может иметь свои

управляющие слова.