28 Архитектура и виды

ввода-вывода в ЭВМ. Способы организации адресного пространства ввода-вывода. Технология plug & play

Архитектура и виды ввода-вывода в ЭВМ. Способы

организации адресного пространства ввода-вывода. Технология plug & play.

Помимо центрального процессора (ЦП) и памяти, третьим

ключевым элементом архитектуры ВМ является система ввода/вывода (СВВ).

СВВ призвана обеспечить обмен информацией между ядром ВМ и периферийными

устройствами.

Две основные функции CВВ:

·

обеспечение

интерфейса с ЦП и памятью;

·

обеспечение

интерфейса с одним или несколькими периферийными устройствами. Можно выделить три

основных способа подключения СВВ к ядру процессора:

CPU отличает устройства по адресам

(не ОП!)=> два уровня адресации.

Адресное пространство системы ввода/вывода

За каждым периферийным устройством закрепляется 3 адреса: RGD, RGC, RGS

(регистр данных команд, состояния). Адреса регистров могут настраиваться.

Регистр состояния чаще всего 1 байт. Если их не хватает – то добавляют «байты

уточненного состояния» - у них отдельные адреса.

Существует 2 способа организации адресного пространства:

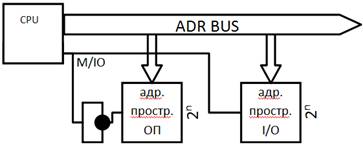

1. С раздельными адресными пространствами для ОП и

устройств в/в.

В шине управления добавляется линия Memory/IO. M/IO=1

соответствует адресу памяти на шине адреса. M/IO=0 соотв. адресу IO. M/IO фактически адресный бит.

Достоинства выделенного адресного пространства:

- адрес внешнего устройства в команде ввода/вывода может

быть коротким. В большинстве СВВ количество внешних устройств намного меньше

количества ячеек памяти. Короткий адрес ВУ подразумевает такие же короткие

команды ввода/вывода и простые дешифраторы;

- программы становятся более наглядными, так как операции

ввода/вывода выполняются с помощью специальных команд;

- разработка СВВ может проводиться отдельно от разработки

памяти.

Недостатки выделенного адресного пространства:

- ввод/вывод производится только через аккумулятор

центрального процессора. Для передачи информации от ВУ в РОН, если аккумулятор

занят, требуется выполнение четырех команд (сохранение содержимого

аккумулятора, ввод из ВУ, пересылка из аккумулятора в РОН, восстановление

содержимого аккумулятора);

- перед обработкой содержимого ВУ это содержимое нужно

переслать в ЦП.

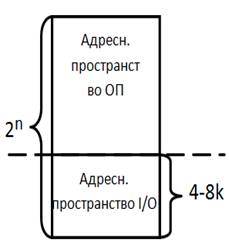

2. I/O с отображением в память.

Достоинства совмещенного адресного пространства:

- расширение набора команд для обращения к внешним

устройствам, что позволяет сократить длину программы и повысить быстродействие;

- значительное увеличение количества подключаемых внешних

устройств;

- возможность внепроцессорного обмена данными между

внешними устройствами, если в системе команд есть команды пересылки между

ячейками памяти;

- возможность обмена информацией не только с аккумулятором,

но и с любым регистром центрального процессора.

Недостатки совмещенного адресного пространства:

- сокращение области адресного пространства памяти;

- усложнение декодирующих схем адресов в СВВ;

- трудности распознавания операций передачи информации при

вводе/выводе среди других операций. Сложности в чтении и отладке программы, в

которой простые команды вызывают выполнение сложных операций

ввода/вывода;

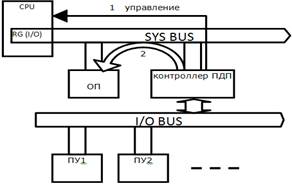

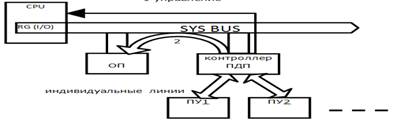

Виды I/O.

Существуют 3 типа:

1. Программно

– управляемый (условный).

2. По

прерываниям.

3. С

прямым доступом к памяти DMA.

1. Программно - управляемый обмен.

Самый простой не требует аппаратной поддержки в CPU, но затраты времени больше.

1) Чтение RGS.

Анализируется бит готовности периферийного устройства.

2) В RGC

команд записывается управляющее слово.

3) Происходит обмен.

Инициатива по ВВ принадлежит CPU.

Инициатива по обмену между регистрами – устройствам ВВ.

Минус – сильная загрузка CPU.

Плюс – хорошо работает с быстрыми устройствами на быстрой

шине.

2. В/в по прерыванию. CPU не

ждет когда устройство готово – оно выдает прерывание. Обработчик прерывания

реализует алгоритм обмена. Лучше подходит для медленных устройств.

Нужно добавить линию INT, средство

формирования вектора прерывания. Более медленный способ (сохранение текущего

состояния при организации прерывания), однако улучшается использование CPU/

Минус – затраты оборудования, ниже скорость обмена.

Плюс – меньше загрузка CPU.

3. Прямой доступ к памяти.

Чтение\запись происходит в два этапа по причине, что команд

для обмена ОП-RG(ПУ) не существует, а существуют две команды (вариант для

записи):

IN RG(IO), I\O и

MOV MEM, RG(IO)

CPU участвует в управление ПДП, но

это участие коротко.

Другие варианты:

Соотношение способов организации ввода/вывода

• Средства,необходимые для организации условного

ввода/вывода, требуются и для ввода/вывода по прерываниям.

• Средства,необходимые

для организации условного ввода/вывода, ввода/вывода по прерываниям, требуются

и при прямом доступе к памяти.

Plug-And-Play

(PNP) -

Букв. вставляй и играй. Технологий автоматического распределения ресурсов

компьютера между его компонентами и периферийными устройствами. Аппаратные

средства Plug and Play - это множество устройств компьютера, которые

автоконфигурируемы операционной системой Plug and Play.

PnP – выполняет

автоматическую инициализацию PnP-устройства то есть назначение ему

адресов ввода-вывода, каналов ПДП и пр. Схема инициализации выглядит следующим

образом:

Подключаемые к PCI устройства

(платы) имеют несколько (зависит от устройства) регистров для конфигурирования,

инициализации и обработки серьезных ошибок. Адресацию к ним обеспечивает конфигурационное

адресное пространство.

Для чтения

конфигурационной информации каждой платы, устройство выбирается, когда сигнал IDSЕL (выбор

устройства инициализации для чтения/записи) активен.

Устройство

обязательно содержит три конфигурационных регистра ADRESS, READ_DATA,

WRITE_DATA.

Во время фазы

адреса конфигурационного цикла конфигурационная шина адресует один из

регистров

Таким образом,

при чтении/записи конфигурационной информации плата выбирается, когда активен

сигнал IDSEL (Initialization Device Select).

Порты WRITE_DATA

и READ_DATA используются для обмена данными с регистрми PnP. Адрес порта

WRITE_DATA

После

конфигурирования устройство не откликается ни на какие сигналы на

конфигурационной шине.

Все шаги

конфигурирования выполняет процедура POST (если BIOS имеет поддержку PnP) или

операционная система при загрузке. PnP BIOS может ограничиться

конфигурированием и активацией только устройств, участвующих в загрузке,

оставляя конфигурирование и активацию дополнительных устройств операционной

системе. BIOS без поддержки PnP может использовать необходимые для загрузки

устройства, сконфигурированные с параметрами по умолчанию, а изоляцией карт,

сбором информации и конфигурированием займется операционная система при

загрузке.