26 Странично-сегментная

организация памяти. Формирование физических адресов. Особенности

сегментно-страничной организация памяти в архитектуре IA – 32.

Для страничной организации в

чистом виде существует проблема сложности управления структурами переменного размера,

по сути это означает две вещи: полную ответственность программиста за

динамические массивы и т.п.; сосуществование стека, кода и данных в одном

линейном адресном пространстве влечет опасность конфликтов между ними.

Для сегментной организации в

чистом виде существуют проблемы с эффективностью использования памяти:

·

Переменный

размер сегмента приводит к сильной фрагментации свободного пространства после

серий подкачек\откачек. Появляется необходимость периодической дефрагментации.

·

Усложнение

алгоритмов замещения.

·

Размер

сегмента может быть очень большим и (на диск)\(с диска) он перемещается

полностью.

·

При

замещении всегда вытесняется равный или больший по размеру сегмент.

Решением проблемы служит сегментно-страничная

организация памяти. В ней размер сегмента выбирается не произвольно, а

задается кратным размеру страницы, даже если одна из страниц сегмента заполнена

частично. Возникает иерархия в организации доступа к данным, состоящая из трех

ступеней: сегмент > страница > слово. Этой структуре соответствует

иерархия таблица служащих для перевода виртуальных адресов в физические. В

сегментной таблице программы перечисляются все сегменты данной программы с

указанием начальных адресов страниц, относящихся к каждому сегменту. Количество

страничных таблиц равно числу сегментов и любая из них определяет расположение

каждой из страниц сегмента в памяти, которые в общем случае располагаются не

подряд а произвольно в физ. памяти, при этом часть страниц может находиться в

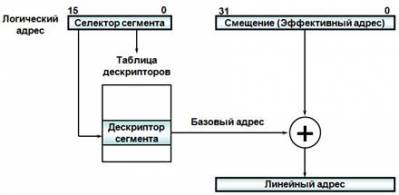

ОП, остальные — во внешней памяти. Структуру виртуального адреса и процесс

преобразования его в физический адрес иллюстрирует рис. 1.

Рис. 1. Преобразование

адреса при сегментно-страничной организации памяти

Производительность такой

организации ниже в 3 раза (из – за 3х обращений к памяти). Основной + данного

метода – при разбиении сегмента на страницы нет нужды загружать в ОП весь

сегмент, т.о. программа написанная для большой ОП будет работать и с маленькой,

но медленнее.

У Intel

используются RG – ы, в которые при обращении к ОП копируется таблица

сегментов и страничная таблица когда её задача становится активной.

Сегментно – страничная

организация памяти в МП Intel.

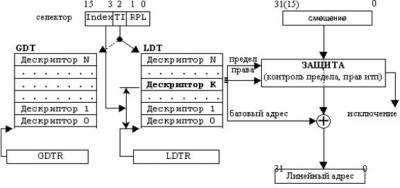

Виртуальная память в Pentium

состоит из дескрипторных таблиц LDT и GDT (локальные и глобальная). Каждая

программа имеет собственную LDT. GDT разделяется всеми

программами. Для доступа к сегменту используется селектор, загруженный в

сегментный регистр (CS,DS,SS,ES,GS). В свою очередь селектор сегмента разделен на поля.

Рис. 3.Преобразование лог.

адр. в линейный адрес.

Логический адрес (виртуальный) состоит из адреса сегмента и смещения.

Смещение формируется суммированием (Intel Base Displacement Scale 1,2,4,8) – в эффективный

адрес.

Линейный адрес образуется сложением базового адреса сегмента с

эффективным адресом. Базовый адрес сегмента образуется содержимым используемого

селекторного регистра сдвигом на 4 влево реальном режиме.

При включении страничной

переадресации она преобразует линейный адрес физическими блоками по 4 Кбайта (у

Pentium размер блока может быть и 4Мбайт).

Сегментно-страничная

организация являетя комдинацией двух сегментной и страничной, которые по

отдельности обладают своими недостатками. В сегментно-страничная организация

памяти размер сегмента выбирается не произвольно, а задается кратным

размеру страницы, даже если одна из страниц сегмента заполнена частично.

Возникает иерархия в организации доступа к данным, состоящая из трех ступеней:

сегмент > страница > слово. Этой структуре соответствует иерархия таблица

служащих для перевода виртуальных адресов в физические. В сегментной таблице

программы перечисляются все сегменты данной программы с указанием начальных

адресов страниц, относящихся к каждому сегменту. Рассмотрим Процесс

Преобразование

логического адреса в линейный

Логический адрес состоит из

двух элементов: селектор сегмента и относительный адрес (смещение). Селектор

сегмента может либо находиться непосредственно в коде команды, либо в одном из

сегментных регистров. Смещение также может либо непосредственно находиться в

коде команды, либо вычисляться на основе значений регистров общего назначения.

Для вычисления линейного

адреса процессор выполняет следующие

действия:

использует селектор сегмента

для нахождения дескриптора сегмента;

анализирует дескриптор

сегмента, контролируя права доступа (сегмент доступен с текущего уровня

привилегий) и предел сегмента (смещение не превышает предел);

добавляет смещение к базовому

адресу сегмента и получает линейный адрес.

Если страничная трансляция

отключена, то сформированный линейный

адрес считается физическим и выставляется на шину процессора для выполнения

цикла чтения или записи памяти.

Селектор - это 16-битный идентификатор сегмента. Он содержит

индекс дескриптора в дескрипторной таблице, бит определяющий, к какой

дескрипторной таблице производится обращение (LDT или GDT), а также запрашиваемые права доступа к сегменту.

Формат селектора:

Index выбирает один из 8192 дескрипторов в таблице

дескрипторов. Процессор умножает значение этого индекса на восемь (длину

дескриптора) и добавляет результат к базовому адресу таблицы дескрипторов.

Таким образом получается линейный адрес требуемого дескриптора.

TI - индикатор таблицы определяет таблицу дескрипторов,

на которую ссылается селектор: TI=0 означает глобальную дескрипторную таблицу (GDT),

а TI=1 - используемую в настоящий момент локальную

дескрипторную таблицу (LDT).

RPL - запрашиваемый уровень привилегий (Requested Privilege Level). Используется механизмом

защиты.

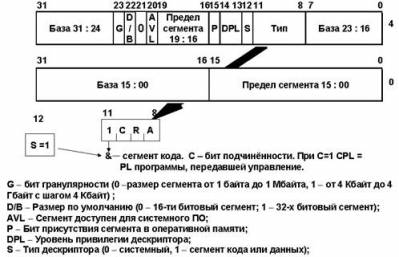

Для вычисления линейного

адреса используются специальные структуры - дескрипторы. Дескриптор -

это 8-байтная единица описательной информации, распознаваемая устройством

управления памятью в защищенном режиме, хранящаяся в дескрипторной таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел

сегмента и права доступа к сегменту. В защищенном режиме сегменты могут

начинаться с любого линейного адреса (который называется базовым адресом

сегмента) и иметь любой предел вплоть до 4Гбайт.

Формат дескриптора:

Базовый адрес сегмента (Base Address)

определяет место сегмента внутри линейного 4Гбайтного адресного пространства.

Процессор объединяет три фрагмента базового адреса для формирования одного

32-разрядного значения.

Предел сегмента (Segment Limit) определяет размер

сегмента. Задает максимальное (для сегментов стека - минимальное) смещение в

сегменте, обращение по которому не вызывает нарушения общей защиты. Процессор

связывает две части поля границы для формирования 20-разрядного результата.

Затем он интерпретирует поле границы одним из двух способов в зависимости от

состояния бита гранулярности: в единицах байт для определения границы до 1Мбайт

(G=0); в единицах страниц по 4Кбайт для определения

границы до 4Гбайт (G=1), при загрузке поле границы сдвигается влево на 12

бит и младшие биты выставляются в 1.

G - бит гранулярности (Granularity)

определяет размер единиц, в которых интерпретируется поле предела. Если G=0,

то граница интерпретируется в байтах, иначе в единицах по 4Кбайт.

D - размер по умолчанию (Default

size). Задает разрядность данных по умолчанию для

дескрипторов сегментов данных или разрядность команд по умолчанию для

дескрипторов сегментов кода: D=0 - 16 бит, D=1 - 32 бит.

AVL (available) - может использоваться по усмотрению системного

программиста.

P - бит присутствия (Present). Если

этот бит очищен, то данный дескриптор не может быть использован при трансляции

адресов. Когда селектор такого дескриптора загружается в регистр сегмента,

процессор переходит к обработке нарушения неприсутствия сегмента.

DPL - уровень привилегий дескриптора (Descriptor Privilege Level) используется механизмом

защиты.

S -

бит системного дескриптора (System): определяет, является ли данный сегмент системным (S=0)

или же сегментом кода/данных (S=1).

Тип дескриптора (Type).

Интерпретация этого поля зависит от вида дескриптора. В дескрипторах сегментов

кода или данных это поле содержит 3-разрядный тип и один бит флага обращения.

Дескрипторы системных сегментов используют все 4 бита.

Флаг обращения (A) устанавливается в дескрипторах сегментов кода и

данных при обращении к сегменту. Операционные системы, реализующие виртуальную

память на уровне сегментов, могут следить за частотой использования сегмента

путем периодической проверки и очистки этого бита.

В качестве сегментов стека

используют сегменты данных, доступные для чтения и записи. Попытка загрузить в SS

селектор незаписываемого сегмента приведет к нарушению общей защиты. Для

динамического изменения размера стека удобно использовать сегменты данных с

расширением вниз (бит E=1). Для таких сегментов предел задает минимальный

адрес, вызывающий нарушение предела сегмента, поэтому уменьшение предела в

таком дескрипторе приведет к добавлению места у вершины стека.

Сегменты кода могут быть либо

обычными, либо подчиняемыми (бит C=1). Передача управления между обычными сегментами

возможна только на одном уровне привилегий. Для подчиняемых сегментов это

правило менее строгое: задача может передать управление на более

привилегированный подчиняемый сегмент кода, но при этом он будет выполняться на

том же уровне привилегий.

Страничная трансляция

Страничное преобразование

действует только в защищенном режиме и включается установкой в 1 бита PG в

регистре CR0.

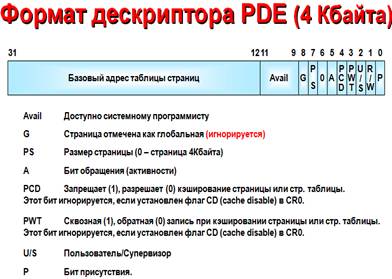

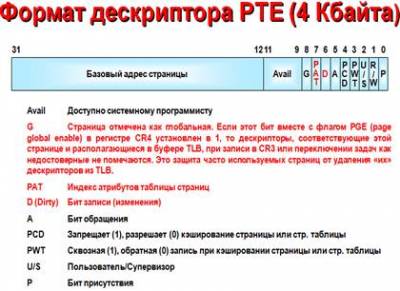

В страничном

преобразовании участвуют два типа структур: каталоги таблиц (Page Directory) и таблицы страниц (Page Table). Эти

структуры состоят из 1024 32-битных элементов. Элементы содержат старшие 20 бит

физического адреса адресуемых объектов. Элементы таблицы страниц (Page Table

Entry - PTE) адресуют страницы, а элементы каталога таблиц (Page Directory

Entry - PDE) адресуют таблицы страниц. Старшие 20 бит физического адреса

каталога таблиц хранится в регистре CR3 (Page Directory Base Register - PDBR).

(Это единственный регистр процессора, который содержит физический адрес

памяти). Все структуры выравниваются по границе страницы.

В процессе страничной

трансляции адресов полученный линейный

адрес разбивается на три части. Старшие десять бит (Directory) линейного адреса

являются индексом элемента из каталога таблиц. По этому элементу определяется

физический адрес таблицы страниц. Биты 21-12 (Table) линейного адреса выбирают

элемент из этой таблицы страниц. Выбранный элемент определяет физический адрес

страницы. Младшие 12 бит (Offset) линейного адреса определяют смещение от

начала страницы.

Страницы начинаются на

границах 4Кбайт областей памяти, поэтому младшие 12 бит адреса страницы всегда

равны нулю. В каталоге таблиц элементы хранят физические адреса таблиц страниц.

В таблице страниц элементы хранят физические адреса самих страниц.

Страницы начинаются на

границах 4Кбайт областей памяти, поэтому младшие 12 бит адреса страницы всегда

равны нулю. В каталоге таблиц элементы хранят физические адреса таблиц страниц.

В таблице страниц элементы хранят физические адреса самих страниц.

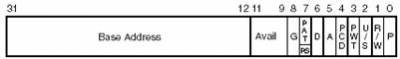

Элементы

каталогов таблиц и таблиц страниц в битах 12-31 содержат старшие 20 бит

физического адреса объекта (для PDE - таблицы страниц, для PTE - страницы).

Биты 9-11 системный программист может использовать по своему усмотрению.

Остальные биты имеют следующие значения:

P - бит присутствия (Present).

Этот бит показывает, может ли элемент таблицы использоваться при трансляции

адреса. Если может, то P=1. Если же P=0 в таблице страниц любого уровня, то

этот элемент нельзя использовать для трансляции адреса и остальные поля

элемента доступны для использования программой. Если P=0 в таблице страниц

любого уровня и сделана попытка использовать этот элемент для трансляции

адреса, то микропроцессор генерирует страничное нарушение (исключение #14).

R/W - бит чтения/записи

(Read/Write). Этот бит определяет тип доступа к странице (для PTE) или группе

страниц (для PDE). Если бит сброшен, страница доступна только для чтения. Если

установлен - для чтения и записи.

U/S - бит уровня привилегий (User/Supervisor). Этот бит

определяет уровень привилегий доступа к станице (для PTE) или группе страниц

(для PDE). Если бит установлен, страница доступна с уровня пользователя. Если

сброшен - только с уровня супервизора.

PWT - бит сквозной записи

(Page Write-Through, 486+). Управляет

кэшированием страниц.

PCD - бит запрещения

кэширования (Page Cache Disable, 486+). Запрещает кэширование страницы или

группы страниц.

A - бит обращения (Accessed).

Процессор устанавливает этот бит всякий раз, когда обращается для чтения или

записи к соответствующей таблице страниц или странице. Процессор самостоятельно

этот бит никогда не сбрасывает.

D - бит изменения (Dirty).

Процессор устанавливает этот бит в PTE всякий раз, когда изменяет содержимое

соответствующей страницы. Процессор самостоятельно этот бит никогда не

сбрасывает. В элементе каталога таблиц этот бит не используется и всегда 0.

Бит 7 PTE: PS - размер

страницы (Page Size, Pentium+). В традиционном страничном преобразовании этот

бит должен быть сброшен. При использовании расширения размера страниц (PSE),

если PS=1, то этот элемент каталога таблиц указывает не на таблицу страниц, а

на страницу размером 4Мбайт (или 2Мбайт, если разрешено PAE).

Бит 7 PDE: PAT - таблица атрибутов страниц (Page Attribute Table Index, Pentium

III+). В процессорах, не поддерживающих

таблицы атрибутов страниц, этот бит должен быть 0.

G - бит глобальности (Global

Page, P6+). Влияет на процесс кэширования страниц. В элементах каталога таблиц

не используется (игнорируется).

Бит изменения (D) и бит

обращения (A) содержат информацию об использовании страницы и устанавливаются

аппаратно. Процессор устанавливает биты доступа в таблицах обоих уровней перед

операцией чтения или записи страницы. Затем процессор устанавливает бит

изменения в таблице страниц второго уровня перед операцией записи по адресу,

соответствующему элементу этой таблицы. Бит изменения в элементах каталога

таблиц не используется.

В операционной системе,

которая поддерживает страничную виртуальную память, эти биты используются для

определения тех страниц, которые могут быть удалены из физической памяти в

случае, когда требуется больший объем, чем размер доступной в данный момент

физической памяти. Ответственность за проверку и очистку этих двух битов лежит

на операционной системе.