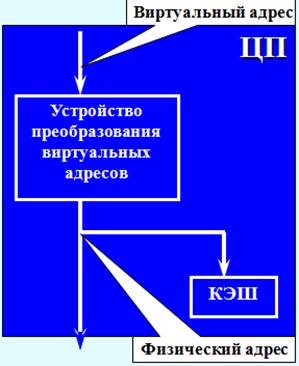

23. Назначение, структурная

организация КЭШ-памяти. Место КЭШа в структуре процессора

•

КЭШ работает с физическими адресами

•

Медленно, поскольку тратится время на преобразование адреса.

•

При прерываниях или переключениях программ не требуется отменять

содержимое КЭШа, т.к. виртуальные адреса в разных программах могут совпадать.

После возврата старая информация может сохраниться. <-

•

КЭШ работает с виртуальными

адресами->

•

Быстро, поскольку не тратится

время на преобразование адреса.

•

При прерываниях или переключениях

программ необходимо отменять содержимое КЭШа, т.к. виртуальные адреса в разных

программах могут совпадать.

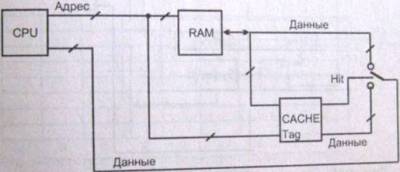

<-Кэш-память запоминает копии инф., передаваемой

между устройствами (меду процессором и основной памятью). Она имеет небольшую

емкость по сравнению с основной памятью и более высокое быстродействие

(реализуется на триггерах).

При чтении данных сначала выполняется обращение к

кэш-памяти. Если в КЭШе имеется копия данных адресованной ячейки основной

памяти, то кэш вырабатывает сигнал hit (попадание) и выдает данные

на общую шину данных. В противном случае этот сигнал не вырабатывается и

выполняется чтение из основной памяти и одновременное помещение считанных

данных в кэш. Эффективность кэширования обуславливается тем, что большинство

прикладных программ удовлетворяют принципу локальности или, иначе говоря, имеют

гнездовой характер обращений, при котором адреса последовательных обращений к

памяти образуют, как правило, компактную группу. Поэтому после первого

обращения к относительно медленной основной памяти повторные обращения уже к

кэшу требуют меньше времени. К тому же при использовании процессором кэш памяти

основная память освобождается, и могут выполняться регенерации данных в

динамическом ЗУ или использование памяти другими устройствами. Объем кэш-памяти

много меньше объема основной памяти и любая информация, помещаемая в кэш должна

сопровождаться дополнительными данными (тегом), определяющими, копией какой

содержания какой ячейки основной памяти она является.

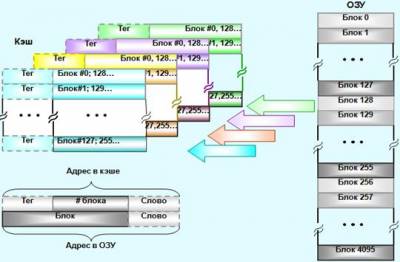

<-В полностью ассоциативной кэш-памяти

каждая ячейка хранит данные, а в теге – полный физический адрес информации,

копия которой записана. При любых обменах физический адрес запрашиваемой

информации сравнивается с полями тег всех ячеек.

эффективное время чтения информации:

Эта формула не совсем точна: так как можно параллельно

считывать и из ОП, и из кэша (если из кэша – удачно, то запрос в ОП -

блокируем).

Существует 2 вида реализации кэша:

1) Фон-неймановская – кэш данных и кода объединены

(более экономически выгодно).

2) Гарвардская - кэш данных и кода разделены. (а может

быть и так: кэша кода мало, а кэш данных – не используется => надо исходить

из тех задач, которые будут ставиться перед ВМ).

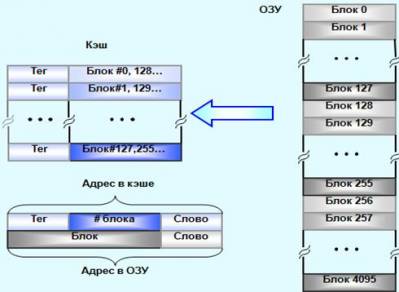

Информация в кэше хранится блоками. Размер блока – 4

или 8 слов (чаще 4). На размер блока влияет несколько факторов. С одной роны,

чем больше блок, тем выше вероятность удачного обращения, но как только

происходит ветвление или безусловный переход, то получаем издержки. То есть чем

больше блок, тем больше вероятность того, что блок придется менять. Кроме того,

есть ограничения по размеру блока: с увеличением его размера увеличивается

количество шин для чтения/записи. Возможен компромисс: блочная передача – механизм

передачи в последовательности адрес – данные – данные – данные – … – конец

блока.

Кроме кэша команд и данных существует адресный кэш: он

хранит адресную информацию отдельными словами (не машинными, а «адресными»).

Буфер TLB – буфер быстрого преобразования адреса – это и есть

организация адресного кэша.

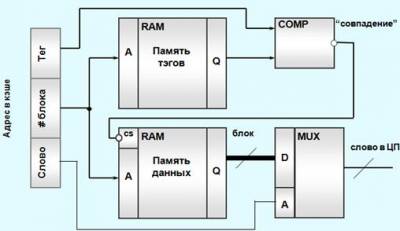

Кэш – ассоциативная память, где в качестве тега

используется адрес, то есть адрес – ключ, а вместе с ним хранятся данные.

Способы отображения памяти:

1. полностью ассоциативного кэш (рис выше).

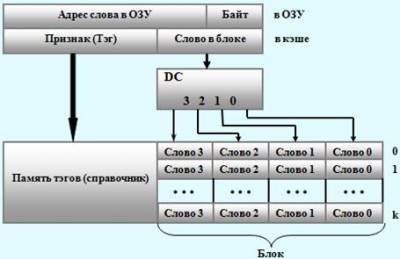

2. Кэш с прямым

отображением в памяти.

Несколько

страниц основной памяти строго соответствуют одной строке кэша

Так как строку в одно и то же время

может занимать только одна страница, нужен специальный ее признак – Тег. Адрес

от процессора делится на 3 части. Младшие разряды (смещение) определяют

положение слова в строке. Средние позволяют выбрать одну из строк в кэш памяти.

Оставшиеся старшие образуют тег. По адресу строки производится считывание. Поле

адресов считанной строки сравнивается с теговым адресом, если есть совпадение – чтение из кэш, нет – из основной памяти.

Достоинство: экономичность. Недостаток: ограничение на

расположение страниц в кэше.

Множественно-ассоциативное отображение.

В этом варианте несколько строк кэша объединяются в

наборы, а средние разряды адреса памяти определяют уже не одну строку, а набор.

Кэш память делится на наборы с небольшим числом строк k, кратным 2.

Страницу основной памяти можно поместить только в тот набор, номер которого

равен адресу страницы по модулю 2n. Место страницы в наборе

может быть произвольным. Сравнение тегов со старшими разрядами адреса

производится только для строк, входящих в набор.

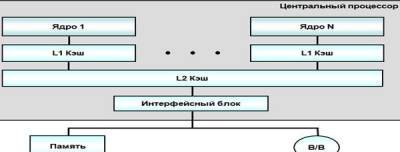

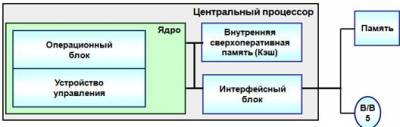

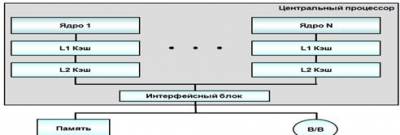

Упрощенная структура процессора

процессора

Простоя многоядерная структура

Многоядерная структура с общей кэш