20. Назначение, функции структуры

контроллеров прерываний. Примеры

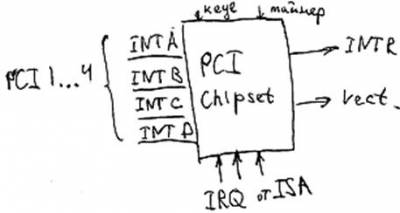

На аппаратном уровне прерывания работают следующим

образом. Когда устройство ввода-вывода заканчивает работу, оно инициирует

прерывание (при условии, что прерывания разрешены ОС). Для этого устройство

выставляет сигнал на выделенную устройству специальную линию шины – линия

запроса. В структуре системы прерываний «с индивидуальными линиями запроса»

(радиальная структура) сколько устройств, столько и линий запроса прерываний, а

значит нужно, чтобы процессор должен иметь столько же входов запроса

прерываний. На практике поступают так: между линиями запроса и процессором есть

промежуточное звено – контроллер прерываний (сокращение PIC).

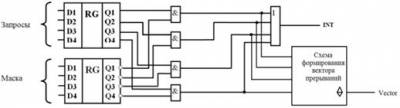

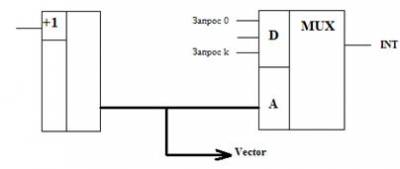

Его назначение в следующем: он должен формировать для процессора 1 бит запроса

прерывания INT и Vector. PIC имеет индивидуальный вход для каждой линии запроса.

PIC

(контроллер) может быть встроен в процессор.

Функции контроллера.

· запоминание запросов

· формирование сигнала INT

· формирование запрета прерываний

·

маскирование

прерываний – то есть запрет обработки некоторых запросов. Пример схемной

реализации:

· формирование Vector

· прием подтверждений о том, что CPU обработал

прерывание

По способам опроса устройств можно выделить следующие

структуры контроллеров:

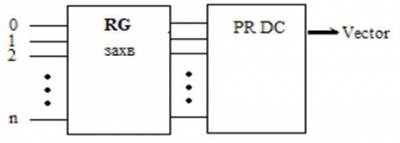

1)

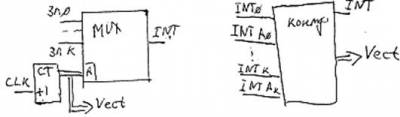

Последовательный опрос – счетчик

непрерывно считает и последовательно опрашивает устройства (в качестве счетчика

может быть регистр сдвига, в котором по кругу бегает «1»). Реализует «круговую

систему приоритетов».

2)

Приоритетный опрос – система с

жесткими приоритетами. Требует приоритетный шифратор (PR DC).

Приоритеты устанавливаются порядком подключения устройств к контроллеру.

3) последовательный опрос.

Пример. – контролер 8259А имеет 8 выходов запросов (IRQ)

и выход запроса INTR, после чего CPU формирует 2 цикла

подтверждения прерывания INTA, во втором цикле контролер передает по DB

8-битный вектор прерывания.