11. Схемно-логические устройства

управления, принцип построения

Схемно – логические УУ представляют собой

логические схемы, вырабатывающие распределенные во времени управляющие

функциональные сигналы. В отличие от управляющих устройств с хранимой в памяти логикой

(микропрограммные УУ) у этих устройств можно изменить логику работы только

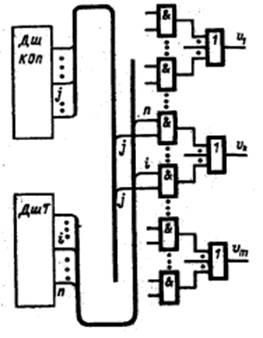

путем переделывания их схем. Типичная схема схемно-логического УУ показана на

рисунке ниже. В состав схемы входят регистр кода операции, являющийся частью

регистра команд, счетчик тактов, дешифратор тактов и дешифратор кода операции,

а также схемы образования управляющих функциональных сигналов.

На счетчик тактов поступают сигналы от

блока синхросигналов, и счетчик с каждым сигналом меняет свое состояние.

Состояния счетчика представляют собой номера тактов, изменяющиеся от 1 до n.

Дешифратор тактов формирует на i-ом выходе единичный сигнал при i-ом

состоянии счетчика тактов, т. е. во время i-го такта.

Дешифратор кода операции вырабатывает единичный сигнал на j-м

выходе, если исполняется j-я команда.

<-Структура управляющей части схемно-лог. УУ.

Логические схемы формирования управляющих

функциональных сигналов для каждой команды возбуждают формирователи

функциональных сигналов для выполнения требуемых в данном такте микроопераций.

Принцип построения логических схем образования

управляющих сигналов поясняется на рисунке 2. Здесь показан фрагмент схемы,

обеспечивающей выработку управляющего сигнала υk

в i–м и n–м тактах выполнения j–й команды.

Рис 2. (ДшКОП – дешифратор Кода операции, ДшТ –

дешифратор тактов)

В общем случае значения управляющих сигналов зависят

еще и от оповещающих сигналов, отражающих ход вычислительного процесса. Для

реализации этих зависимостей элементы, представленные на рис 2, берутся

многоходовыми и на них заводятся требуемые сигналы логических условий.

Серьезным недостатком рассмотренной схемы является

одинаковое число тактов для всех команд. Это требует выравнивания числа тактов

исполнения команд по наиболее «длинной» команде, что ведет к непроизводительным

затратам времени. Чтобы устранить этот недостаток, схемы строят с

использованием нескольких счетчиков тактов. Схема формирования тактовых

сигналов (датчик тактовых сигналов) может строится на основе использования

регистра сдвига, по которому двигается одна 1 (регистр с «бегущей единицей»),

что не требует использования дешифратора.

Существует 4 пути проектирования схемно – логических

УУ:

1.

На основе интерпретации

микропрограмм конечными автоматами (КА). Работу операционного блока можно

описать микропрограммой, например, на языке микроопераций или в виде графа. По

микропрограмме строится соответствующий управляющий автомат типа Мура или Мили.

КА ведет за собой применение синхронных триггеров.

2.

Использование описания поведения

последовательных схем (логических).

3.

Построение по временным

диаграммам.

4.

Использование эвристических

методов.

Преимущества схемно – логических УУ:

·

Быстрее

микропрограммных.

·

Проще

для простых алгоритмов.

Недостатки схемно – логических УУ:

·

Нерегулярная

структура (каждый раз её приходится проектировать заново).

·

Немодернизуемость.