09. Классификация, структуры, функции

устройств управления

Устройство

управления (УУ) —

важнейшая часть ВМ, организующая автоматическое выполнение программ (путем

реализации функций управления) и обеспечивающая функционирование ВМ как единой

системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность

элементов, между которыми происходит пересылка информации, в ходе которой эта

информация может подвергаться определенным видам обработки. Пересылка

информации между любыми элементами ВМ инициируется своим сигналом управления

(СУ), то есть управление вычислительным процессом сводится к выдаче нужного

набора СУ в нужной временной последовательности. Основной функцией УУ является

формирование управляющих сигналов, отвечающих за извлечение команд из памяти в

порядке, определяемом программой, и последующее исполнение этих команд. Кроме

того, УУ формирует СУ для синхронизации и координации внутренних и внешних

устройств ВМ. Генерируемая управляющим

устройством последовательность управляющих сигналов задается поступающими на

входы устройства кодом операции, сигналами из операционного блока, несущими

информацию об особенностях операндов, промежуточных и конечного результатов

операции, а также синхросигналами, задающими границы тактов.

Классифицировать УУ можно по различным признакам: по

уровню централизации, по типам длительности тактов в УУ, по реализации хранения

алгоритмов микроопераций.

По

уровню централизации:

·

Централизованные

(УУ – один в ВМ)

·

Децентрализованные

(в каждом блоке – свой УУ)

·

Смешанные

(1+2 – конвейеров лучше)

По

типам длительности тактов:

·

Синхронизованные.

Длительность такта = const.

·

Асинхронные.

И длительность такта и цикла – переменные. Это обеспечивает самое высокое

быстродействие, но возникают сложности в настройке.

Для

организации:

·

Используют

признак завершения операции.

·

Группируют

микрооперации – по признаку длительности (в каждой группе – свое время

выполнения).

·

Синхронно

– асинхронные. Длительность такта = const, длительность

цикла – переменная (из-за разного количества тактов)

Входной информацией для центрального БУ

служит код операции текущей команды, который определяет конкретную выполняемую

операцию. Он поступает в БУ из регистра команд и служит для выработки сигналов

управления, передаваемых на все узлы и устройства компьютера.

Помимо кода операции при работе БУ

используются флаги, т. е. признаки, характеризующие результаты выполнения

предшествующей операции. Они необходимы для организации выполнения команд

условного перехода. Блок управления вырабатывает сигналы при поступлении на

него тактовых импульсов. Кроме того, он получает сигналы от системной шины,

например запросы прерывания, подтверждения приема информации и т. п.

Блок управления формирует управляющие

сигналы, направляемые в различные устройства и блоки компьютера, прежде всего в

процессор. Эти сигналы служат для управления перемещением данных между

регистрами, работой устройств, инициирования тех или иных функций. Сигналы

управления направляются также в шину для передачи в блоки памяти и на

устройства ввода-вывода.

Действия в

операционном блоке в течение одного такта называются микрооперациями (МО), а

любая операция или команда, выполняемая за несколько тактов, описывается

некоторой микропрограммой, определяющей последовательность действий при

выполнении этой команды. Сигналы управления, формируемые БУ и поступающие на

входы операционного устройства, вызывают в нем выполнение микрооперации.

Поскольку блоки управления формируют сигналы для выполнения микроопераций, их

часто называют микропрограммными автоматами.

В зависимости от

способа формирования сигналов управления микрооперациями различают два типа

микропрограммных автоматов: с «жесткой» и программируемой логикой.

Устройства управления

с «жесткой» логикой. Код операции и номер такта в управляющем автомате с

«жесткой» логикой (рис. 5.8) поступают на дешифраторы DC и затем на логические

схемы формирования сигналов управления. На эти же схемы, представляющие собой

наборы схем совпадения, поступают различные осведомительные сигналы, которые

характеризуют результат выполнения: предыдущей операции или микрооперации.

Сигналы для каждой

микрооперации в автомате с «жесткой» логикой формируются своим собственным

набором логических схем, который невозможно изменить, не меняя всю систему

управления компьютером, что и обусловливает название автомата. В состав его

схемы входят счетчик и дешифратор тактов, дешифратор кода операции и логические

схемы формирования сигналов управления. Время срабатывания этих логических схем

мало, поэтому такие аппаратно реализованные микропрограммные автоматы

обеспечивают наибольшее быстродействие. Однако их сложность возрастает с расширением

системы команд, так как для каждой операции в них должен быть предусмотрен

собственный набор схем.

Эти особенности

автоматов с «жесткой» логикой привели к тому, что они находят применение в

RISC-процессорах, а в компьютерах с расширенной системой команд обычно

используют иной подход — микропрограмму, хранимую в специальной памяти.

Второй тип управляющего

автомата — автомат с хранимой в памяти логикой. Управление каждой операцией,

входящей в систему команд компьютера, осуществляется с помощью хранимых в

памяти слов. Эти управляющие слова, или микрокоманды, содержат информацию о

микрооперациях, выполняемых в течение одного машинного такта и осуществляющих

элементарное преобразование над данными, и указание, где находится следующая микрокоманда.

Такое управление получило название микропрограммного.

Микропрограммы для

каждой команды компьютера можно разместить в специальной памяти микропрограмм.

Таким образом, процесс командного управления становится двухступенчатым:

сначала нужно извлечь из основной памяти компьютера команду, а затем для ее

выполнения извлечь из памяти микропрограмм последовательность микрокоманд. Для

реализации такого двухступенчатого процесса требуется быстрая постоянная память

довольно большого объема.

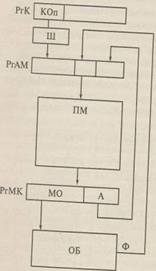

Основное место в

типичной структуре устройства управления с хранимой в памяти логикой (рис. 5.9)

занимает память микропрограмм (ПМ), в которой находятся все выполняемые

микрокоманды. Она является постоянной памятью; адрес очередной микрокоманды

(РгАМ) определяется кодом текущей операции (КОп из регистра команд

преобразуется шифратором Ш), флагами Ф, полученными при выполнении предыдущей

операции (из регистра флагов), и адресной частью предыдущей микрокоманды

(А).Очередная МК считывается из памяти и заносится в регистр RGмк,

откуда СУ МО поступают в ОБ.

Обобщенная структура

управления

В

обобщенной структуре УУ (рис. 6.3) можно выделить две части: управляющую и

адресную. Управляющая

часть УУ предназначена для координирования работы операционного блока ВМ,

адресной части устройства управления, основной памяти и других узлов ВМ. Адресная часть УУ

обеспечивает формирование адресов команд и исполнительных адресов операндов

в основной памяти.

В состав управляющей части УУ входят:

* регистр команды

(РК), состоящий из адресной (Адрес) и операционной (КОп, СА) частей;

*микропрограммный автомат (МПА); * узел прерываний и приоритетов (УПП)

Регистр команды РК

предназначен для приема очередной команды из запоминающего устройства.

Микропрограммный автомат на основании результатов расшифровки операционной

части команды (КОп, СА) вырабатывает определенную последовательность

микрокоманд, вызывающих выполнение всех целевых функций УУ.

Узел

прерываний и приоритетов позволяет реагировать на различные ситуации, связанные

как с выполнением рабочих программ, так и с состоянием ВМ.

Адресная

часть УУ включает в себя:

*операционный

узел устройства управления (ОПУУ); *регистр адреса (РгА); *счетчик команд (СК).

Регистр

адреса используется для хранения исполнительных адресов операндов, а счетчик

команд — для выработки и хранения адресов команд. Содержимое РгА и СК

посылается в регистр адреса основной памяти (ОП) для выборки операндов и

команд соответственно.

ОПУУ, называемый иначе узлом

индексной арифметики или узлом адресной арифметики, обрабатывает адресные части

команд, формируя исполнительные адреса операндов, а также подготавливает адрес

следующей команды при выпол